The annual IEDM conference (www.ieee-iedm.org), sponsored by the IEEE Electron Devices Society, usually includes presentations covering noteworthy technological developments, and this year’s event is no exception. To be held December 1-5, 2018 at the

Hilton San Francisco Union Square Hotel, it includes a talk by researchers from the National Institute of Advanced Industrial Science and Technology (AIST) who describe a superjunction silicon-carbide power device exhibiting a super-low on-resistance and a high blocking voltage.

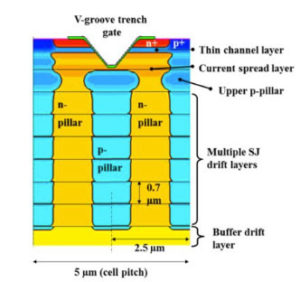

As a quick review, a superjunction (SJ) device is a type of MOSFET attractive for applications where fast switching at high voltages is a key requirement. Instead of traditional well-shaped cells, SJ devices have pillar-shaped cells which extend deeply into a thicker epitaxial layer for better performance at smaller scales.

A team from Japan’s AIST will report on how they were able to realize the lowest specific on-resistance ever seen in a SiC power transistor with a blocking voltage exceeding 600 V. It was an 1,170-V superjunction SiC device that realized an Ron,sp of 0.63 mΩ-cm2. This performance came through the use of a V-shaped groove in the channel to reduce channel resistance, and by improving the charge balance among the pillars.

Though the advantages of a V-shaped groove have been described previously, the researchers say these are the best numbers ever reported and represent notable progress in the ongoing effort to obtain the best trade-off possible between specific on-resistance and breakdown voltage in power devices.

Leave a Reply