It can be challenging to give a highly dynamic load a stable voltage when the power supply sits several feet away from the device under test.

Bill Griffith • Keysight Technologies

Today’s integrated circuits put a highly dynamic load on their power supply. This behavior poses a challenge during testing when IC power comes from programmable power supplies. The high-frequency current waveforms can lead to voltage drops at the integrated circuit. If severe enough, the voltage drop can, for example, reset a microprocessor or cause anomalous test results. It is important to understand why the voltage drop arises and how to minimize the voltage drop.

First consider the type of supply powering the DUT. The best possible output voltage regulation traditionally comes from linear power supplies. However, linear supplies tend to be large, expensive, and highly inefficient.

First consider the type of supply powering the DUT. The best possible output voltage regulation traditionally comes from linear power supplies. However, linear supplies tend to be large, expensive, and highly inefficient.

Recent advances in switching technology make it possible to replace linear supplies with switching power supplies in performance applications. Switching supply designers face seemingly contradictory goals of low output noise, fast transient response, low cost, and high density. Low output noise usually comes thanks to multiple filtering stages or larger filter components. This approach can be expensive and exhibits a slow transient response. It also is characterized by a low power density because of the size of the components. More advanced power supplies employ higher switching frequency, better filter design, and more sophisticated control topologies to optimize all the criteria. When selecting a power supply for IC testing, it is essential to examine the voltage transient response specification and output impedance to ensure good performance.

Optimizing load wiring

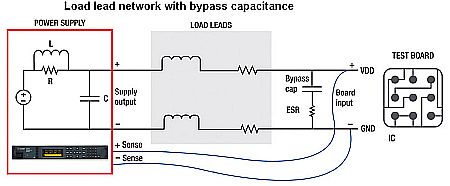

In many cases, physical constraints force the power supply to sit several feet away from the IC test board, necessitating at least a few feet of load-lead wiring. Load lead wiring impedance can quickly degrade the source impedance the IC sees. Almost all programmable power supplies provide sense lead inputs. These let the operator make the point of voltage regulation be the location of the sense leads.

In an IC testing application, the sense point would be as close as possible to the IC. However, the voltage regulation loop can suppress voltage transients at this sense point only within its control bandwidth. Consequently, a voltage transient can happen at this sense point if the current transient rises sufficiently fast. Load lead impedance at these lower frequencies can be modeled as a lumped series inductance and resistance.

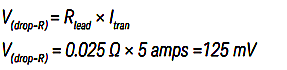

Let’s examine a 25-A application with 5-A transients where the power supply is set to 2.5 V and connected to the IC test board via five feet of 14 AWG wire. Because this is a low-voltage application, voltage undershoots greater than 100 mV are generally unacceptable. The 14 AWG wiring has 2.5 mΩ/ft of resistance, so the round-trip connection between the power supply output and the IC test board has 25 mΩ of resistance.

The power supply voltage-control loop will compensate the calculated 125 mV drop after a period commensurate with its bandwidth. However, in the meantime, the IC will experience this 125 mV of voltage drop. In this application, the effect of the load lead resistance alone is enough to cause an unacceptable short-duration drop at the test board. However, the load lead inductance is another major cause of voltage drop. It is not uncommon for the test board to ramp the 5-A transient in 10 μsec. This high rate of current change can cause a constant voltage drop across the leads during the current ramp. Load lead inductance changes depending on the loop area formed by the positive and negative lead. Using an approximation of the inductance, you can estimate the voltage drop. In most cases, 250-nH/ft inductance is a good model for non-twisted load wiring.

The power supply voltage-control loop will compensate the calculated 125 mV drop after a period commensurate with its bandwidth. However, in the meantime, the IC will experience this 125 mV of voltage drop. In this application, the effect of the load lead resistance alone is enough to cause an unacceptable short-duration drop at the test board. However, the load lead inductance is another major cause of voltage drop. It is not uncommon for the test board to ramp the 5-A transient in 10 μsec. This high rate of current change can cause a constant voltage drop across the leads during the current ramp. Load lead inductance changes depending on the loop area formed by the positive and negative lead. Using an approximation of the inductance, you can estimate the voltage drop. In most cases, 250-nH/ft inductance is a good model for non-twisted load wiring.

Combining the effect of the resistance and inductance leads to:

The result of 1.375 V is unacceptable. As mentioned previously, the power supply voltage regulation loop will sense this voltage transient and adjust the supply output enough to maintain a steady 2.5 V at the test board. However, this process can take up to a millisecond even with a high-quality power supply. To reduce the lead inductance, tightly couple the force leads together by either tying them at regular intervals or by simply twisting them together. Twisting the leads also provides the added benefit of better immunity to other magnetic fields potentially caused by different load leads carrying large current transients. A good model for twisted leads is a 170-nH/ft inductor. This inductor includes both the positive and negative lead inductance effects. Recalculation with twisted leads yields:

Although the voltage drop has diminished, the total result is still unacceptable. Further improvement can be had by paralleling cable runs. For example, paralleling four sets of twisted cables will reduce the resistance and inductance by a factor of four.

The goal of 100 mV is still out of reach, especially considering that the power supply will contribute an additional transient voltage drop in response to the change in output current. More specialized cabling options such as custom coaxial cables or flat wire cables can reduce the inductance to as low as 10 nH/ft. However, these options are costly and not as readily available. An alternative is low-impedance energy storage located close to the test board.

Using a local bypass capacitor

The power supply cannot compensate rapidly enough for the voltage drop across load leads and the drop across its output, so you need a local source of energy. Capacitors are well suited to provide low impedance at high frequencies to complement the power supply low impedance provided at low frequencies. Many different capacitor technologies are available, and the process of finding the right part or a combination of components can be difficult.

Ceramic capacitors are well suited for high-frequency bypassing at low voltages. However, even with recent advances in ceramic capacitor technologies, they cannot match the high density and low price of aluminum electrolytic and conductive polymer aluminum solid electrolytic capacitors. The equivalent series resistance of the bypass network is an essential parameter because it appears in series with the capacitor and can make the bypass network significantly less effective. Selecting a capacitor with the lowest possible voltage will help keep ESR low and capacitance density high.

Ceramic capacitors are well suited for high-frequency bypassing at low voltages. However, even with recent advances in ceramic capacitor technologies, they cannot match the high density and low price of aluminum electrolytic and conductive polymer aluminum solid electrolytic capacitors. The equivalent series resistance of the bypass network is an essential parameter because it appears in series with the capacitor and can make the bypass network significantly less effective. Selecting a capacitor with the lowest possible voltage will help keep ESR low and capacitance density high.

The interaction between the power supply voltage-control loop, the load-lead network, and the bypass capacitance can be a bit complex. However, some simple approximations can help with the initial value selection for the capacitor.

Calculate peak network impedance

Determine the desired peak impedance of the load lead network and bypass capacitance using the following expression:

![]()

Set the desired peak impedance equal to the expression for the characteristic impedance of the L-C tank formed by the load lead inductance and the bypass capacitance. Solve the expression for the value of capacitance:

The power supply must have an output impedance lower than the characteristic impedance of the L-C tank. Otherwise the calculation will not predict system behavior. The power supply output impedance will drop with decreasing frequency. In a case where the power supply output impedance is higher than the desired peak impedance, pick a tank resonant frequency to equal the frequency at which the power supply output impedance is less than or equal to Zpeak. The resonant frequency must be lowered by use of a larger bypass capacitor.

Proper damping of the resonant tank is crucial. An improperly damped tank will tend to ring and can also destabilize the power supply control loop. The combination of the load lead resistance and capacitor ESR will damp the resonant tank. We will target a damping ratio of 0.5 for faster response and lower peak voltage by equating the tank resistance to the L-C tank characteristic impedance.

It may not be possible to find one capacitor with the right capacitance and ESR, but you can use parallel combinations  of capacitors with different values and ESRs to arrive at the desired parameters.

of capacitors with different values and ESRs to arrive at the desired parameters.

The nearby figure shows the transient voltage response observed at the load when using the Keysight N7950A dynamic dc power supply. It excels in low-voltage, high-current situations and exhibits a low output impedance, perfect for this application. The light blue trace represents the four twisted pairs of cables without a local capacitor. Dark blue is the response from adding a 530 µF capacitor, as calculated in Equation 7. Boosting the capacitance by four times drops the tank impedance by a factor of two and yields the results shown in red.

Although load-lead impedance of lengthy cable runs can severely degrade the transient response performance of a high-performance power supply, mitigation practices can help realize the required performance. Twisting load-lead wiring to minimize the loop area formed between the supply and return lines, use of flat copper, or heavy gauge coaxial cables can significantly reduce the load-lead inductance. Properly sizing a bypass capacitor network at the DUT can further improve voltage level stability in the face of fast DUT current transients.

Leave a Reply